# SiC MOSFET 栅源回路参数的串联扰动研究

#### 张宇,李先允,王书征,唐昕杰,袁宇,卢乙

(南京工程学院 电力工程学院,江苏 南京 211167)

摘要:为了使SiC MOSFET工程运用时避免串联扰动的威胁,研究栅源回路参数对串联扰动的影响是很有必要的。研究通过对栅源回路参数的调控,将串联扰动现象分为正压尖峰与负压尖峰两部分进行分析,确定影响串扰电压尖峰的参数,为驱动回路参数设计提供方向性意见。首先建立拓扑简化模型,理论分析影响电压尖峰的栅源回路参数,随后搭建实验平台进行电压尖峰观测以及对理论分析进行实验验证,最后对实验波形进行分析。实验表明,当驱动电阻为 $0~20~\Omega$ 、驱动杂散电感为 $0~300~\mathrm{nH}$ 、栅极电容为 $0~10~\mathrm{nF}$ 时,串联扰动随着桥臂自身驱动电阻、驱动杂散电感的增大而增大、随着栅极电容的增大而减小。此外,负载阻抗会影响负压尖峰,尖峰震荡同样会影响器件正常工作。

关键词:碳化硅MOSFET;栅源回路;串联扰动;电压尖峰

中图分类号:TM131.2 文献标识码:A DOI:10.19457/j.1001-2095.dqcd21595

#### Research on Series Disturbance of SiC MOSFET Gate-source Loop Parameters

ZHANG Yu, LI Xianyun, WANG Shuzheng, TANG Xinjie, YUAN Yu, LU Yi

(School of Electric Power Engineering, Nanjing Institute of Technology, Nanjing 211167, Jiangsu, China)

Abstract: In order to avoid the threat of series disturbance during the engineering application of SiC MOSFET, it is necessary to study the influence of driving circuit parameters on the series disturbance. Based on the adjustment of the gate-source loop parameters, the series disturbance phenomenon was divided into two parts in this study: positive pressure spike and negative pressure spike. First, a simplified topology model was established, and the gate-source loop parameters that affect voltage spikes were theoretically analyzed. Then an experimental platform was set up to observe the voltage spikes and verify the theoretical analysis. Finally, the experimental waveforms were analyzed. Experiments show that when the driving resistance is  $0\sim20~\Omega$ , the driving stray inductance is  $0\sim300~\mathrm{nH}$ , and the gate capacitance is  $0\sim10~\mathrm{nF}$ , the series disturbance increases with the increase of the driving resistance and driving stray inductance of the bridge arm, but it decreases as the gate capacitance increases. In addition, negative pressure spikes will be affected by load impedance, normal operation of the device will also be affected by the spike oscillation.

**Key words:** silicon carbide metal-oxide-semiconductor field-effect transistor (SiC MOSFET); gate-source loop; series disturbance; voltage spike

现如今,新能源发电、电动汽车以及开关电源等领域的发展趋向于高效率、高转化率以及高可靠性。这使得以碳化硅(silicon carbide,SiC)器件为首的宽禁带半导体器件以其高开关频率、低开关损耗、低散热需求等优点得到越来越多的关注[1-3]。SiC 材料的热导系数是 Si 材料的 2.5 倍,饱和电子漂移率是 Si 的 2 倍,所以 SiC 器件能在更高的频率、更高的开断速度下工作。现如今对SiC 器件的研究主要集中在 SiC MOSFET,与传统

Si MOSFET相比,SiC MOSFET具有更快的开断速度,更高的功率密度,更高的正向耐压,更低的散热需求[4-6],并且栅源两端具有良好的反向耐压能力(第一代 SiC MOSFET可承受-5V,第二代 SiC MOSFET可承受-10V)[2],由于其卓越的性能,SiC MOSFET在中、高压领域出现了代替 Si IGBT的趋势[7-8]。但是随着电压水平和开关速度的提升,电路中寄生参数所带来的扰动现象将更加严重,这将威胁系统的安全运行[9-10]。虽然依靠新的 PCB

制作工艺以及封装技术可以有效地减少寄生参数的大小,但是SiC MOSFET也依然面临着串联扰动以及电磁干扰和电磁应力的风险[11],这些负面效应会在一定程度上加速器件老化,严重时甚至造成器件损坏。串联扰动现象主要存在于换流器上、下桥臂结构中,当上桥臂开通时,过高的du/dt作用在下桥臂器件寄生电容上会产生正压尖峰,正压尖峰超过阈值电压时会造成器件的误导通,这将影响系统整体的安全性[12-14]。当上桥臂关断时,积累在寄生电容中的能量得到释放会产生负压尖峰,负压尖峰小于器件栅极耐受值时,会造成器件的损坏。

综上所述,基于栅源回路参数的调控,对器件串联扰动现象进行分析研究[15],得到串联扰动的影响因素,这对SiC MOSFET的工程应用具有极大的意义。本文首先基于串联回路中的单个桥臂进行驱动回路简化分析,建立数学模型,得到影响串联扰动的各个因素,然后搭建平台进行实验验证,最后对实验波形进行进一步分析。

# 1 简化建模分析

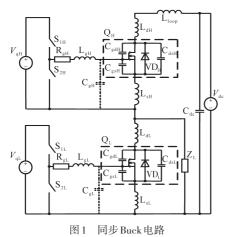

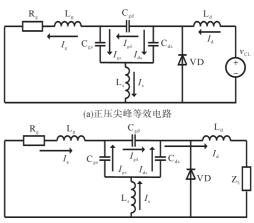

图1为典型同步Buck电路。图1中,上、下桥臂功率开关器件Q<sub>H</sub>,Q<sub>L</sub>均为SiC MOSFET;C<sub>gs</sub>,C<sub>gd</sub>,C<sub>ds</sub>为SiC MOSFET封装寄生电容;C<sub>dc</sub>为滤波电容;L<sub>d</sub>,L<sub>s</sub>,L<sub>s</sub>,L<sub>loop</sub>为杂散电感;Z<sub>L</sub>为负载;R<sub>s</sub>为栅极电阻,由驱动电阻和栅源回路寄生电阻组成;C<sub>g</sub>为外加栅极电容,用于栅源电容C<sub>gs</sub>的调控,理论分析时不参与讨论;V<sub>q</sub>为驱动电压;V<sub>dc</sub>为母线电压。本文通过研究上桥臂SiC器件快速开断时,下桥臂器件栅源两端产生的电压尖峰来研究串联扰动现象,文中将串联扰动分为两个阶段分析,其中,第一阶段产生正压尖峰,第二阶段产生负压尖峰。图2为串联扰动等效电路,图3为对应的简化等效电路。

Fig.1 Synchronous Buck circuit

(b)负压尖峰等效电路

图2 串联扰动等效电路

Fig.2 Series disturbance equivalent circuit

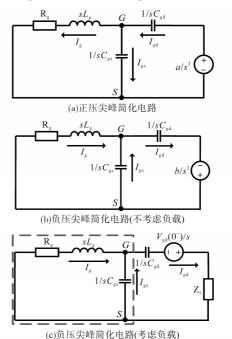

图 3 简化等效电路 Fig.3 Simplified equivalent circuit

1.8.0 componed equivalent encun

#### 1.1 栅源回路参数对正压尖峰的影响

当 $Q_H$ 快速导通时, $Q_L$ 漏源两端电压 $v_{ds}$ 瞬间由 0升高至母线电压 $V_{dc}$ ,过高的 du/dt作用在 $C_{gd}$ 上 将产生漏电流 $I_{gd}$ ,并对 $C_{gs}$ 进行充电,使 $C_{gs}$ 上形成一个正的电压尖峰,正压尖峰等效电路具体如图 2a 所示。其中, $I_{gd}$ , $I_{gs}$ , $I_{ds}$ 分别为电容 $C_{gd}$ , $C_{gs}$ 和 $C_{ds}$ 上的电流; $I_{g}$ , $I_{d}$ , $I_{g}$ 分别为器件栅、漏、源极流过的电流; $v_{CL}$ 等效为上桥臂开通瞬间作用在下桥臂器件漏源两端的电压(不考虑器件导通电阻的变化),由上桥臂开断速度和母线电压 $V_{dc}$ 共同决定,可近似等效为

$$v_{\rm CL} = \begin{cases} at & t_{\rm on} > t > 0 \\ V_{\rm dc} & t > t_{\rm on} \end{cases} \tag{1}$$

其中  $a=V_{de}/t_{on}$  式中: $t_{on}$ 为下桥臂漏源电压上升时间。

因漏电流  $I_a$ 较小,所以在  $L_a$ 上形成的压降相对于母线电压可以忽略。  $L_s$ 包括器件栅极引脚杂散电感和驱动回路寄生电感。  $L_s$ 为器件源极引脚杂散电感,其值较小,近似计算时可以忽略。 二极管 VD 在串扰形成时反向截止,不参与工作。电容  $C_{ds}$ 的大小不会影响作用在电容  $C_{gd}$ 和  $C_{gs}$ 串联支路上的电压,又因电容电流 i=C du/dt,所以电容  $C_{ds}$ 对电流  $I_{gs}$ 的值没有影响,分析栅源电压  $v_{gs}$ 时可以忽略。对正压尖峰等效电路进行简化以及 Laplace 变换,假设储能原件初始能量为 0,具体如图 3a 所示。

根据基尔霍夫定律对图 3a 进行节点电压方程的列写:

$$\begin{cases} I_{\rm gd} = I_{\rm gs} + I_{\rm g} \\ I_{\rm gd} = (\frac{a}{s^2} - v_{\rm gs}) s C_{\rm gd} \\ I_{\rm gs} = v_{\rm gs} s C_{\rm gs} \\ I_{\rm g} = \frac{v_{\rm gs}}{R_{\rm g} + s L_{\rm g}} \end{cases} \tag{2}$$

点G,S分别为器件栅、源极,解得:

$$v_{\rm gs} = \frac{aC_{\rm gd}(R_{\rm g} + L_{\rm g}s)}{(C_{\rm gd} + C_{\rm gs})L_{\rm g}s^3 + (C_{\rm gd} + C_{\rm gs})R_{\rm g}s^2 + s}$$

(3)

进行Laplace 逆变换,并假设:

$$\begin{cases} A = \sqrt{(C_{\rm gs} + C_{\rm gd})R_{\rm g}^2 - 4L_{\rm g}} \\ B = \sqrt{(C_{\rm gs} + C_{\rm gd})R_{\rm g}^2 - 4L_{\rm g}} / \sqrt{C_{\rm gs} + C_{\rm gd}} L_{\rm g} \\ C = C_{\rm gs} + C_{\rm gd} \end{cases}$$

(4)

解得:

$$v_{gs} = aC_{gd} \left[ \frac{(2L_{g} - R_{g}^{2}C)(e^{Bt} - 1)}{2A\sqrt{C} \cdot e^{\frac{R_{g}^{t}}{2L_{g}} + \frac{Bt}{2}}} - \frac{2A\sqrt{C} \cdot e^{Bt} + 1 - 2e^{\frac{R_{g}^{t}}{2L_{g}} + \frac{Bt}{2}}}{2A\sqrt{C} \cdot e^{\frac{R_{g}^{t}}{2L_{g}} + \frac{Bt}{2}}} \right]$$

(5)

以 SiC MOSFET 器件 C2M0080120D 为例,输入电容  $C_{iss}$ =950 pF 且随  $v_{ds}$ 变化较小,栅漏电容电容  $C_{gd}$  随着  $v_{ds}$ 的增大迅速降低,取  $C_{gd}$ =15 pF。当器件工作电压  $V_{dc}$ =500 V 时,假设栅源电压上升时间为49 ns,串扰等效电源的系数  $a=1.53\times10^7$  V/s,驱动电压为+20/-5 V,改变栅源回路参数得到正压尖峰幅值如表 1 所示。

#### 表 1 不同栅源回路参数下的正压尖峰幅值

Tab.1 Spike amplitude of positive pressure under different grid-source loop parameters

| 栅极电容/          | 栅极电感/<br>nH       | 正压尖峰幅值/V                 |                          |                          |

|----------------|-------------------|--------------------------|--------------------------|--------------------------|

| nF             |                   | $R_{\rm g}$ =10 $\Omega$ | $R_{\rm g}$ =20 $\Omega$ | $R_{\rm g}$ =30 $\Omega$ |

| $C_{\rm g}$ =0 | $L_{\rm g}$ =50   | 1.52                     | 2.92                     | 3.88                     |

|                | $L_{\rm g}$ =150  | 1.58                     | 3.13                     | 4.07                     |

|                | $L_{\rm g} = 300$ | 2.46                     | 3.65                     | 4.41                     |

| $C_{\rm g}$ =1 | $L_{\rm g}$ =50   | 1.50                     | 2.28                     | 2.68                     |

|                | $L_{\rm g}$ =150  | 1.81                     | 2.44                     | 2.78                     |

|                | $L_{\rm g} = 300$ | 2.31                     | 2.69                     | 2.93                     |

| $C_{\rm g}$ =5 | $L_{\rm g}$ =50   | 0.91                     | 1.06                     | 1.13                     |

|                | $L_{\rm g}$ =150  | 1.01                     | 1.10                     | 1.15                     |

|                | $L_{\rm g} = 300$ | 1.09                     | 1.14                     | 1.17                     |

由表1分析可得,当上桥臂开断速度和母线电压不变,即a为定值时,正压尖峰幅值随着驱动电阻  $R_{\rm g}$ 、杂散电感  $L_{\rm g}$ 的增大而增大,随着寄生电容  $C_{\rm gs}$ 增大而减小,其中  $C_{\rm gs}$ 可以通过栅极电容  $C_{\rm g}$ 进行调控。

### 1.2 栅源回路参数对负压尖峰的影响

当 $Q_H$ 快速关断时, $Q_L$ 漏源两端电压 $v_{ts}$ 由母线 电压V<sub>dc</sub>迅速降为0,积累在电容C<sub>ed</sub>上的能量开始 释放并形成漏电流 $I_{sd}$ ,当漏电流流经 $C_{ss}$ 时将在栅 源电容上形成一个负的电压尖峰,具体如图 2b 所 示。图 2b 为负压尖峰等效电路,其中 Z 为负载,  $I_{L}$ 为流过负载的电流。由于 $C_{ls}$ 放电过程中电流  $I_{ts}$ 不经过电容 $C_{ss}$ ,讨论 $v_{ss}$ 的时候可以忽略。杂散 电感 L 仅为引脚杂散电感,其值过小,近似计算 时可以省略。Cer放电时二极管VD反向截止,仅 在放电结束时为L,提供续流通道, 当忽略负载Z, 以及线路杂散电感的影响,仅针对栅源回路对正 压尖峰等效电路进行简化以及 Laplace 变换,具体 如图 3b 所示。其中,系数  $b=V_{de}/t_{eff}$ ,下桥臂漏源电 压下降时间t<sub>of</sub>由上桥臂关断速度决定,现假设系 数 b 为定值。根据基尔霍夫定律对图 3b 进行节 点电压方程的列写:

$$\begin{cases} I_{\rm gd} = I_{\rm gs} + I_{\rm g} \\ I_{\rm gd} = (\frac{b}{s^2} + v_{\rm gs}) s C_{\rm gd} \\ I_{\rm gs} = -v_{\rm gs} s C_{\rm gs} \\ I_{\rm g} = -\frac{v_{\rm gs}}{R_{\rm g} + s L_{\rm g}} \end{cases}$$

(6)

对式(6)进行求解,得:

$$v_{\rm gs} = -\frac{bC_{\rm gd}(R_{\rm g} + L_{\rm g}s)}{(C_{\rm gd} + C_{\rm gs})L_{\rm g}s^3 + (C_{\rm gd} + C_{\rm gs})R_{\rm g}s^2 + s}$$

(7)

联立式(4)对式(7)进行Laplace逆变换,得:

$$v_{\rm gs} = bC_{\rm gd} \left[ \frac{AR_{\rm g} \sqrt{C} \left( e^{Bt} + 1 - 2e^{\frac{R_{\rm g}^t}{2L_{\rm g}} + \frac{Bt}{2}} \right)}{2A\sqrt{C} \cdot e^{\frac{R_{\rm g}^t}{2L_{\rm g}} + \frac{Bt}{2}}} - \frac{2A\sqrt{C} \cdot e^{\frac{R_{\rm g}^t}{2L_{\rm g}} + \frac{Bt}{2}}}{2A\sqrt{C} \cdot e^{\frac{R_{\rm g}^t}{2L_{\rm g}} + \frac{Bt}{2}}} \right]$$

当器件工作电压 $V_{dc}$ =500 V时,假设器件关断速度为40 ns,理想状态下栅漏电容放电系数b=  $1.87\times10^7$  V/s,改变栅源回路参数得到负压尖峰幅值如表2所示。

表2 不同栅源回路参数下的负压尖峰幅值

Tab.2 Spike amplitude of negative pressure under different grid-source loop parameters

| 栅极电容/<br>nF   | 栅极电感/nH ·         | 负压尖峰幅值/V                 |                          |                          |

|---------------|-------------------|--------------------------|--------------------------|--------------------------|

|               |                   | $R_{\rm g}$ =10 $\Omega$ | $R_{\rm g}$ =20 $\Omega$ | $R_{\rm g}$ =30 $\Omega$ |

| $C_{ m g}$ =0 | $L_{\rm g}$ =50   | -1.88                    | -3.42                    | -4.34                    |

|               | $L_{\rm g} = 150$ | -2.39                    | -3.79                    | -4.61                    |

|               | $L_{\rm g}$ =300  | -3.63                    | -4.47                    | -5.04                    |

| $C_{ m g}$ =1 | $L_{\rm g} = 50$  | -1.78                    | -2.49                    | -2.83                    |

|               | $L_{\rm g}$ =150  | -2.21                    | -2.68                    | -2.94                    |

|               | $L_{\rm g} = 300$ | -2.69                    | -2.93                    | -3.09                    |

| $C_{ m g}$ =5 | $L_{\rm g} = 50$  | -0.96                    | -1.08                    | -1.13                    |

|               | $L_{\rm g}$ =150  | -1.05                    | -1.12                    | -1.15                    |

|               | $L_{\rm g} = 300$ | -1.12                    | -1.15                    | -1.17                    |

由表 2 可知, 当系数 b 为定值时,  $v_s$  负压尖峰幅值随栅极电阻  $R_s$ 、栅极电感  $L_s$  的增大而增大, 栅极电容  $C_s$  增大,即栅源电容  $C_s$  增大时, 负压尖峰幅值变化减小。

#### 1.3 负载电阻对负压尖峰的影响

当不考虑负载电阻时, $v_{ds}$ 的下降时间  $t_{off}$ 主要由上桥臂器件的关断速度决定,具体如 1.2 节所述。但由图 2b 可知,在同步 Buck 电路中,负压尖峰阶段  $C_{gd}$ 释放能量时将会经过负载电阻  $Z_{L}$ ,假设电容  $C_{ed}$ 放电初始为恒压源,有:

$$I_{\rm gd} = \frac{v_{\rm gd}}{Z_{\rm L} + Z_{\rm g}} \tag{9}$$

式中: $Z_s$ 为栅源回路阻抗。

当  $Z_L$ 增大时, $I_{gd}$ 随之下降,由  $Q_{gd}=C_{gd}V_{dc}=I_{gd}t_{off}$ 可知,当电容两端电压和储存电荷不变时, $C_{gd}$ 的放电时间  $t_{off}$ 将会随之增大( $t_{off} \ge t_f$ , $t_f$ 为上桥臂器件关断时间),电容  $C_{gd}$ 放电转为自由放电,电压下降速度不再由  $t_f$ 决定,此时负压尖峰简化电路如图 3c 所示。由于图中标记部分端口结构未发生变

化,输入电流  $I_{gd}$ 减小会使负压尖峰幅值降低, $t_{off}$ 增大使负压尖峰持续时间增大,同时两者共同作用使得调控寄生电感  $L_g$ 对负压尖峰幅值的影响降低。本文主要讨论栅源回路对串联扰动的影响,故对负载的影响不做深入研究。

# 2 实验验证

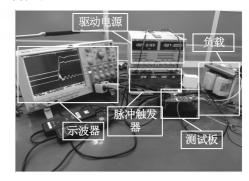

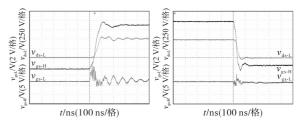

搭建如图 4 所示的同步 Buck 电路实验平台进行电压尖峰观察及上述推导的实验验证。实验采用 Tektronix 公司生产的 DPO4054B 示波器及其配套电压探头 TPP0500 和 P5205A, SiC MOSFET 采用 CREE 公司的 C2M0080120D, 续流二极管为 SiC 肖特基二极管 C4D20120D, 触发脉冲由Firstack 公司生产的脉冲触发仪提供。图 5 为电压尖峰实验波形,由于负载电阻的存在,负压尖峰幅值较小,实验波形同时也证实本次实验平台的正确性。

图4 实验平台

Fig.4 Experiment platform

图 5 电压尖峰 Fig.5 Voltage spike

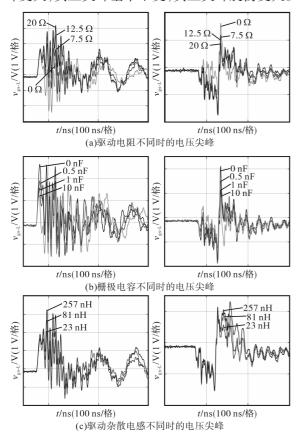

对上述理论分析进行实验验证,为了保护器件安全运行,基础测试电压 $V_{dc}$ 选为500 V,驱动电阻 $R_{g}$ 为5 $\Omega$ ,栅极电容 $C_{g}$ 为1 nF,栅极电感 $L_{g}$ 为0,负载电阻 $Z_{L}$ 为50 $\Omega$ 。图6为改变栅源回路参数时的电压尖峰波形,为了清晰地表达波形变化,仅展示部分参数,其中左图均为正压尖峰波形,右侧均为负压尖峰波形。图6a为驱动电阻分别为0 $\Omega$ ,7.5 $\Omega$ ,12.5 $\Omega$ ,20 $\Omega$ 时的电压尖峰波形。由图6a可得,当驱动电阻增大时,正、负压尖峰均

增大,负压尖峰震荡变小,这是由于驱动电阻与栅极电容形成RC滤波,降低震荡。图6b为栅极电容分别为0nF,0.5nF,1nF,10nF时的电压尖峰波形,由图6b可得,当栅极电容增大时,正、负压尖峰均变小,负压尖峰震荡也变小。图6c为栅极电感分别为23nH,81nH,257nH时的电压尖峰波形,由图6c可得,当栅极杂散电感增大时,正压尖峰变大,负压尖峰基本不变,负压尖峰震荡变大。

图 6 改变栅源回路参数时的电压尖峰

Fig.6 Voltage spike with different gate-source loop parameters

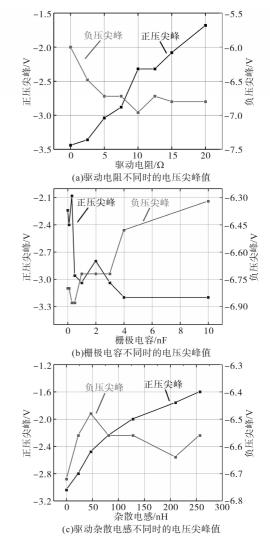

图7为不同栅源回路参数的电压尖峰值,统计了改变栅源回路参数时的所有实验结果。由图7可得,当驱动电阻为0~20 Ω,仅驱动电阻增大其他条件不变时,正、负压尖峰均增大。栅极电容为0~10 nF时,随着栅极电容的增大,正、负压尖峰均减小。栅极电感为0~300 nH时,栅极杂散电感增大,正压尖峰增大,负压尖峰基本不变。其中,正压尖峰幅值变化较大,负压尖峰幅值变化较小,这与负载电阻的接入有关。

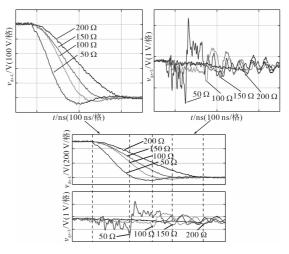

由1.3节推导可知,当其它条件不变时,负载 电阻的大小会影响负压尖峰幅值的大小和持续 时间,现通过实验进行验证。不同负载电阻时, 器件漏源电压 v<sub>4</sub>及负压尖峰之间的关系如图 8 所

图7 不同栅源回路参数的电压尖峰值

Fig.7 Voltage spikes of different gate-source loop parameters 示,由图 8 可见,当负载电阻增大时, $v_{\rm ds}$ 下降时间也增大,同时负压尖峰持续时间正比于 $v_{\rm ds}$ 下降时间,幅值大小正比于 $dv_{\rm ds}/dt_{\rm off}$ 。

图 8 不同负载电阻的负压尖峰

Fig.8 Negative voltage spikes with different load resistances

对上述实验分析可得,通过对栅源回路参数的调控可以达到调节电压尖峰的目的,与前文理论分析结果一致。为了同时满足 SiC MOSFET驱动的快速性与安全性,驱动回路设计时 PCB 布局注意降低寄生参数,驱动参数选择时,建议降低驱动电阻的大小,利用增大栅极电容来降低器件高速开断过程中的过冲与震荡现象。以 Buck 电路为例,负载的大小会影响负压尖峰幅值以及持续时间,换流器正常运行时建议工作在满载状态。

## 3 总结

本文基于栅源回路参数调控对SiC器件串联 扰动现象进行分析研究并进行实验验证,结果表明:

- 1)器件所受的串联扰动现象是器件高速开 断形成的 du/dt 作用在相邻器件封装寄生电容上 引起的,可以通过栅源回路参数和负载阻抗进行 调控。

- 2)电压尖峰随着驱动电阻、杂散电感的增大 而增大,随着栅极电容的增大而减小,较大的负 载电阻有利于降低负压尖峰。驱动电路设计中 应该降低驱动电阻的大小,通过提高栅极电容来 抑制开关震荡。

- 3)伴随电压尖峰出现的尖峰震荡也对器件 安全产生威胁,还需进一步研究。

#### 参考文献

- [1] Parthasarathy Nayak, Kamalesh Hatua. Parasitic inductance and capacitance-assisted active gate driving technique to minimize seitching loss of SiC MOSFET[J].IEEE Transactions on Industrial Electronics, 2017, 64 (10):8288-8298.

- [2] Feng Gao, Qi Zhou, Panrui Wang, et al. A gate driver of SiC MOSFET for suppressing the negative voltage spike in a bridge

- circuit[J]. IEEE Transactions on Power Electronics, 2018, 33 (3):2339 -2353.

- [3] 彭咏龙,江涛,李亚斌,等.SiC MOSFET高频感应加热电源系统研究[J].电气传动,2017,47(3):70-73.

- [4] 张斌锋,许津铭,钱强,等.SiC MOSFET特性及其应用的关键技术分析[J].电源学报,2016,14(4):39-48.

- [5] 邹世凯,胡冬青,黄仁发,等. SiC MOSFET驱动电路设计与 实验分析[J].电气传动,2017,47(9):59-63.

- [6] 马保慧.基于Si和SiC器件的逆变器系统性能对比研究[J]. 电气传动,2017,47(8):3-6,48.

- [7] Hazra S, De A, Bhattacharya S, et al. High switching performance of 1.7 kV, 50 A SiC power MOSFET over Si IGBT for advanced power conversion applications[J]. IEEE Transactions on Power Electronics, 2016, 31(7):4742-4754.

- [8] 李磊印,宁圃奇,温旭辉,等.1200V碳化硅MOSFET与硅IGBT器件特性对比性研究[J].电源学报,2016,14(4):32-38

- [9] 马小亮.混合模块及其应用[J].电气传动,2016,46(4):3-7.

- [10] 巴腾飞,李艳,梁美. 寄生参数对SiC MOSFET 栅源极电压影响的研究[J]. 电工技术学报,2016,31(13):64-73.

- [11] Liu T, Ning R, Wong T T Y, et al. Modeling and analysis of SiC MOSFET switching oscillations[J].IEEE Journal of Emerging & Selected Topics in Power Electronics, 2017, 4(3):747–756.

- [12] 李辉, 黄樟坚, 廖兴林, 等. 一种抑制 SiC MOSFET 桥臂串扰 的改进门极驱动设计[J]. 电工技术学报, 2019, 34(2): 275-285

- [13] Wang J, Chung S H. A novel RCD level shifter for elimination of spurious turn-on in the bridge-leg configuration[J]. IEEE Transactions on Power Electronics, 2015, 30(2):976–984.

- [14] Zhang Z, Wang F, Tolbert L M, et al. Active gate driver for fast switching and crosstalk suppression of SiC devices in a phaseleg configuration[C]//IEEE Applied Power Electronics Conference and Exposition(APEC), Charlotte, NC, USA, 2015:15–19.

- [15] 曾正, 邵伟华, 陈昊, 等. 基于栅极驱动回路的 SiC MOSFET 开关行为调控[J]. 中国电机工程学报, 2018, 28(4): 1165-1176.

收稿日期:2020-03-08 修改稿日期:2020-03-17